|

Banc

de recherche pour le

test des semi-conducteurs.

Le Challenge:

Le

test des semi-conducteurs sur tranche de silicium (wafer) nécessite

d'établir un contact électrique avec les circuits gravés sur la plaque.

Ce contact est établi physiquement via ce que l'on appelle une "carte

à

pointes". Le

test des semi-conducteurs sur tranche de silicium (wafer) nécessite

d'établir un contact électrique avec les circuits gravés sur la plaque.

Ce contact est établi physiquement via ce que l'on appelle une "carte

à

pointes".

Une carte à

pointe est un ensemble de pointes de quelques dizaines de micromètres de

diamètre qui sont solidaires les unes des autres et qui sont disposées

suivant une configuration propre au circuit à

tester.

Chaque fois qu'un contact

électrique est établi entre les pointes de la carte à

pointes et les pads de connexion des circuits, une fraction du matériau

constituant ces pads est arraché, polluant ainsi les pointes et la

plaque de silicium par des débris de matière. Ces débris de matière

s'accumulent sur les pointes et finissent par dégrader la qualité du

contact électrique (Rcontact).

Afin de garder les

pointes propres et d'éviter au mieux la pollution de la plaque par des

débris de matière les pointes doivent être régulièrement nettoyées en

les insérant dans un matériau abrasif retenant les débris. La résistance

de contact retrouve alors une valeur faible.

Si les pointes ne sont

pas nettoyées assez régulièrement le rendement des puces bonnes sur la

plaque chute car des circuits sont alors rejetés à tort. Si le nettoyage

a lieu trop souvent le temps de test et l'usure des cartes à pointes

augmente ce qui augmente le coût du test. Il convient donc de déterminer

la fréquence de nettoyage optimale des pointes de test. Celle-ci peut

varier dans de grandes proportions en fonction des matériaux

constituants les pads et les pointes de test mais aussi en fonction des

procédés de fabrication des circuits.

Afin d'optimiser

rapidement les paramètres de nettoyage des pointes de test et d'étudier

les interactions entre les pointes et les pads de test d'une part et les

interactions entre les pointes et les matériaux de nettoyage d'autre

part il fallait construire un banc permettant de simuler le test des

semi-conducteurs et permettant la mesure des paramètres dont l'accès

n'est pas possible sur une chaîne de test en production.

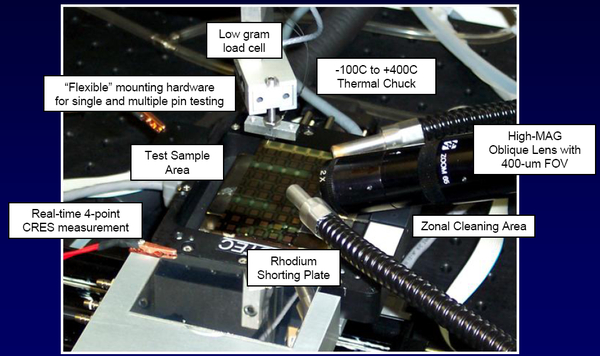

Le matériel:

- Un capteur de force

Transducer Techniques relié à

une carte d'acquisition

National Instruments permettant de mesurer la

pression de la pointe sur le pad de test. Le capteur de force est

lui-même solidaire d'un actionneur en Z permettant de lever ou de

baisser la pointe sur le pad de test et d'effectuer ainsi des touchdowns.

- Un chuck régulé en

température (-100 a +400 degrés Celsius) fourni par

Instec. Le substrat

de silicium contenant les circuits à

tester est maintenu au chuck par vide d'air. Le chuck est monté sur une

table X-Y permettant de le déplacer et d'amener ainsi sous la pointe de

test les pads de test ou les matériaux de nettoyage.

- Un contrôleur d'axe

National Instruments PCI-7334 équipé d'une unité de puissance MID

7604 pour le contrôle des actionneurs X, Y et Z.

- Un

sourcemetre Keithley

K2400 afin de réaliser des mesures électriques en tension ou courant et

caractériser ainsi le Cres.

- Une camera vidéo haute

résolution reliée à une carte Firewire NI-IEEE 1394.

La solution:

- Un instrument de recherche

unique dans le domaine du test des semi-conducteurs avec une interface

logicielle implémentée en LabVIEW permettant de réaliser les fonctions

suivantes:

- Mesure de la force

nécessaire à

l'insertion des pointes de test dans les matériaux de nettoyage.

- Mesure de la résistance

de contact en fonction de la force appliquée à la pointe.

- Visualisation de

l'accumulation des débris sur les pointes en fonction du nombre de

touchdowns.

- Visualisation de

l'usure des pointes en fonction du nombre de touchdowns dans le matériau

de nettoyage.

- Simulation des

fonctions de probing

permettant de reproduire en laboratoire les conditions de test

rencontrées en production.

Pour en savoir plus sur

ce banc de recherche vous pouvez télécharger la présentation suivante

sur le site de l'IEEE

Semiconductor Wafer Test Workshop:

- "Novel

Methodologies for Assessing On-line Probe Process Parameters"

(J. Broz, B. Blanc, G. Humphrey, R. Moore, P. Mui)

- "Optimisation

des procédés de test des semi-conducteurs" (Brice Blanc,

Solutest)

|